Intel, Micron Stack New Memory Technology

Chipmakers Intel Corp. and Micron Technology are claiming a new class of memory technology based on new materials and a three-dimensional "cross point" architecture said to deliver a 1,000-fold increase in non-volatile memory speeds.

The partners said on Tuesday (July 28) their 3-D XPoint non-volatile memory technology is ten times denser than conventional memory chips. They also claimed the design represents the first new class of memory chips since the introduction of NAND flash more than 25 years ago.

The new memory technology is targeted at datacenters in general and applications and services specifically that would benefit from "fast access to large sets of data," the partners said. The non-volatile memory technology serves essentially as "memory pool" for system memory and storage.

As service providers balance cost, power and performance tradeoffs to help customers cope with mountains of data, 3-D XPoint technology is being positioned as combining the performance, density, power and cost advantages associated with current memory technologies. Hence, Intel and Micron are touting the memory technology as 1,000 times faster than conventional memory technologies and 1,000 times the write endurance of NAND.

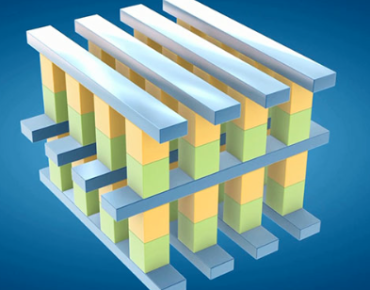

The new memory chip architecture leverages 3-D technology that allows thin layers of memory to be stacked to boost cell density. While 3-D stacking has been around for more than a decade, Intel and Micron said they developed a "cross point structure" in which perpendicular wires connect submicron columns. The architecture allows any individual memory cell to be addressed by selecting the top or bottom wire.

Intel and Micron developed stackable "memory grids" to maximize cell density. The "cross point architecture" (top and bottom wires in white) provides access to each memory cell, eliminating the need for transistors.

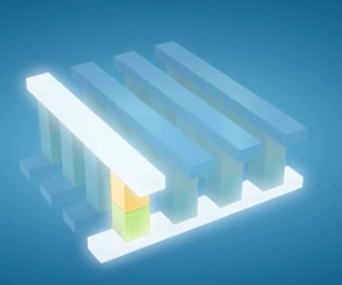

Further, the architecture creates a "three-dimensional checkerboard" in which memory cells are positioned at the intersection of word and bit lines. That high-density configuration allows memory cells to be addressed individually. Hence, data could be written and read in small chunks, speeding up the read/write process, the companies said.

In another twist, the chipmakers developed a "selector" that enables a 3-D Xpoint memory cell to be written to or read without requiring a transistor. By contrast, DRAM technology requires a transistor at each memory cell, adding to the chip's size and cost. (The partners also noted that DRAM density is no longer doubling every two years, meaning the technology is "hitting a wall.") The amount of voltage sent to each selector eliminated the requirement for transistors.

The result, the partners claimed, is a stackable, transistor-less design with up to 10 times greater density than volatile memory technology in the same space. Meanwhile, current nonvolatile NAND technology is slower than DRAM technology.

Latency remains a technology hurdle as datacenters are stuffed to the rafters. Intel and Micron claim the new non-volatile memory technology significantly reduces the lag time between memory, stored data and processing, allowing more data to be stored closer to processors and boosting access speeds "to enormous data sets" beyond the performance delivered by other non-volatile storage technologies.

The partners said latency for 3-D Xpoint technology is measured in "10s of nanoseconds" compared to "10s of microseconds" for current NAND technology. That performance boost would help eliminate the bottleneck between processors and stored data sets, they claimed. Hence, the partners are initially targeting the memory technology at high-performance SSD storage.

Intel and Micron said they would begin sampling 3-D XPoint technology later this year, and each company is currently developing unspecified products based on the memory advance.

Related

George Leopold has written about science and technology for more than 30 years, focusing on electronics and aerospace technology. He previously served as executive editor of Electronic Engineering Times. Leopold is the author of "Calculated Risk: The Supersonic Life and Times of Gus Grissom" (Purdue University Press, 2016).